## **HCPL-4200**

# Optically Coupled 20 mA Current Loop Receiver

# **Data Sheet**

#### **Description**

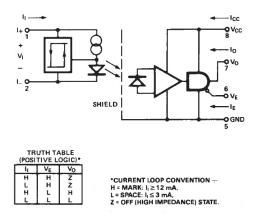

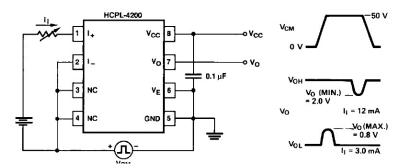

The HCPL-4200 optocoupler is designed to operate as a receiver in equipment using the 20 mA Current Loop. 20 mA current loop systems conventionally signal a logic high state by transmitting 20 mA of loop current (MARK), and signal a logic low state by allowing no more than a few milliamperes of loop current (SPACE). Optical coupling of the signal from the 20 mA current loop to the logic output breaks ground loops and provides for a very high common mode rejection. The HCPL-4200 aids in the design process by providing guaranteed thresholds for logic high state and logic low state for the current loop, providing an LSTTL, TTL, or CMOS compatible logic interface, and providing guaranteed common mode rejection. The buffer circuit on the current loop side of the HCPL-4200 provides typically 0.8 mA of hysteresis which increases the immunity to common mode and differential mode noise. The buffer also provides a controlled amount of LED drive current which takes into account any LED light output degradation. The internal shield allows a guaranteed 1000 V/µs common mode transient immunity.

#### **Functional Diagram**

#### **Features**

- Data output compatible with LSTTL, TTL and CMOS

- 20 K Baud data rate at 1400 metres line length

- Guaranteed performance over temperature (0°C to 70°C)

- · Guaranteed On and Off thresholds

- · LED is protected from excess current

- Input threshold hysteresis

- · Three-state output compatible with data buses

- · Internal shield for high Common Mode Rejection

- Safety approval UL recognized -3750 V rms, for 1 minute CSA approved

- Optically coupled 20 mA current loop transmitter, HCPL-4100, also available

#### **Applications**

- · Isolated 20 mA current

- · Loop receiver in:

- Computer peripherals Industrial control equipment Data communications equipment

A 0.1 µF bypass capacitor connected between pins 8 and 5 is recommended.

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

## **Ordering Information**

HCPL-4200 is UL Recognized with 3750 Vrms for 1 minute per UL1577.

|             | Op                | otion                 |                    |               |           |             |               |

|-------------|-------------------|-----------------------|--------------------|---------------|-----------|-------------|---------------|

| Part number | RoHS<br>Compliant | Non-RoHS<br>Compliant | Package            | Surface Mount | Gull Wing | Tape & Reel | Quantity      |

| HCPL-4200   | -000E             | No option             | 300 mil<br>- DIP-8 |               |           |             | 50 per tube   |

|             | -300E             | #300                  |                    | X             | Χ         |             | 50 per tube   |

|             | -500E             | #500                  |                    | Х             | Χ         | χ           | 1000 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

#### Example 1:

HCPL-4200-500E to order product of Gull Wing Surface Mount package in Tape and Reel packaging in RoHS compliant.

#### Example 2:

HCPL-4200 to order product of 300 mil DIP package in tube packaging and non-RoHS compliant.

Option datasheets are available. Contact your Avago sales representative or authorized distributor for information.

Remarks: The notation '#XXX' is used for existing products, while (new) products launched since 15th July 2001 and RoHS compliant option will use '-XXXE'.

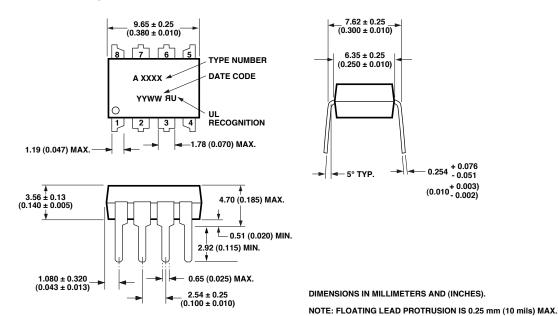

## Package Outline Drawings — 8 Pin DIP Package (HCPL-4200)

8 Pin DIP Package with Gull Wing Surface Mount Option 300 (HCPL-4200)

LEAD COPLANARITY = 0.10 mm (0.004 INCHES).

NOTE: FLOATING LEAD PROTRUSION IS 0.25 mm (10 mils) MAX.

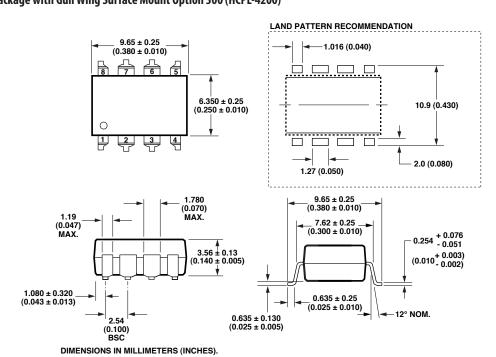

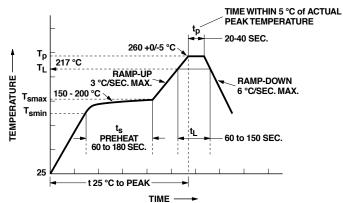

## **Solder Reflow Thermal Profile**

Note: Non-halide flux should be used.

Figure 1a. Solder Reflow Thermal Profile.

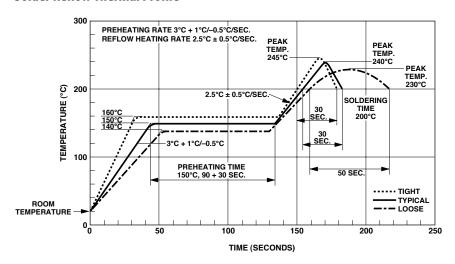

## **Recommended Pb-Free IR Profile**

NOTES:

THE TIME FROM 25 °C to PEAK TEMPERATURE = 8 MINUTES MAX.

$T_{smax} = 200 \, ^{\circ}C, \ T_{smin} = 150 \, ^{\circ}C$

Note: Non-halide flux should be used.

Figure 1b. Pb-Free IR Profile.

## **Regulatory Information**

The HCPL-4200 has been approved by the following organizations:

#### UL

Recognized under UL 1577, Component Recognition Program, File E55361.

#### **CSA**

Approved under CSA Component Acceptance Notice #5, File CA 88324.

# **Insulation and Safety Related Specifications**

| Parameter                                           | Symbol | Value | Units | Conditions                                                                                                                                                |

|-----------------------------------------------------|--------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Min. External Air Gap<br>(External Clearance)       | L(IO1) | 7.1   | mm    | Measured from input terminals to output terminals, shortest distance through air                                                                          |

| Min. External Tracking Path<br>(External Creepage)  | L(IO2) | 7.4   | mm    | Measured from input terminals to output terminals, shortest distance path along body                                                                      |

| Min. Internal Plastic Gap<br>(Internal Clearance)   |        | 0.08  | mm    | Through insulation distance, conductor to conductor, usually the direct distance between the photoemitter and photodetector inside the optocoupler cavity |

| Tracking Resistance<br>(Comparative Tracking Index) | CTI    | 200   | volts | DIN IEC 112/VDE 0303 PART 1                                                                                                                               |

| Isolation Group                                     |        | Illa  |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                                              |

Option 300 – surface mount classification is Class A in accordance with CECC 00802.

# **Absolute Maximum Ratings**

(No Derating Required up to 70°C)

| 55°C to +125°C              |

|-----------------------------|

|                             |

| 6 mm below seating plane)   |

| 0 V to 20 V                 |

| 30 mA to 30 mA              |

| 0.5 A <sup>[1]</sup>        |

| 0.5 V to 20 V               |

| 0.5 V to 20 V               |

| 25 mA                       |

| 90 mW <sup>[2]</sup>        |

| 210 mW <sup>[3]</sup>       |

| 255 mW <sup>[4]</sup>       |

|                             |

| see Fig. 1, Thermal Profile |

|                             |

# **Recommended Operating Conditions**

| Parameter                        | Symbol          | Min. | Max. | Units     |

|----------------------------------|-----------------|------|------|-----------|

| Power Supply Voltage             | V <sub>cc</sub> | 4.5  | 20   | Volts     |

| Forward Input Current<br>(SPACE) | I <sub>sı</sub> | 0    | 2.0  | mA        |

| Forward Input Current<br>(MARK)  | I <sub>MI</sub> | 14   | 24   | mA        |

| Operating Temperature            | T <sub>A</sub>  | 0    | 70   | °C        |

| Fan Out                          | N               | 0    | 4    | TTL Loads |

| Logic Low Enable<br>Voltage      | $V_{_{\rm EL}}$ | 0    | 0.8  | Volts     |

| Logic High Enable<br>Voltage     | $V_{\rm EH}$    | 2.0  | 20   | Volts     |

**DC Electrical Specifications** For  $0^{\circ}\text{C} \leq T_{A} \leq 70^{\circ}\text{C}$ ,  $4.5 \text{ V} \leq V_{CC} \leq 20 \text{ V}$ ,  $V_{E} = 0.8 \text{ V}$ , all typicals at  $T_{A} = 25^{\circ}\text{C}$  and  $V_{CC} = 5 \text{ V}$  unless otherwise noted. See note 13.

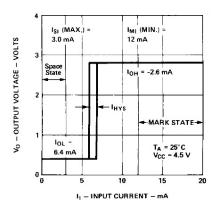

| Parameter                          | Symbol           | Min. | Тур.  | Тур. Мах. |       | Test Conditions                                                     | Fig.       | Note |

|------------------------------------|------------------|------|-------|-----------|-------|---------------------------------------------------------------------|------------|------|

| Mark State Input<br>Current        | I <sub>MI</sub>  | 12   |       |           | mA    |                                                                     | 2, 3,<br>4 |      |

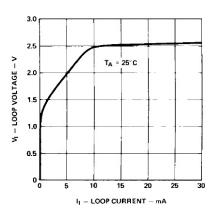

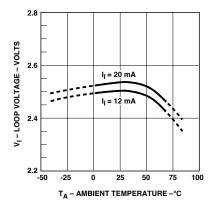

| Mark State Input<br>Voltage        | $V_{MI}$         |      | 2.52  | 2.75      | Volts | $I_1 = 20 \text{ mA}$ $V_E = Don't Care$                            | 4, 5       |      |

| Space State Input<br>Current       | I <sub>SI</sub>  |      |       | 3         | mA    |                                                                     | 2, 3,<br>4 |      |

| Space State Input<br>Voltage       | $V_{\rm SI}$     |      | 1.6   | 2.2       | Volts | $I_1 = 0.5$ to 2.0 mA $V_E = Don't$ Care                            | 2, 4       |      |

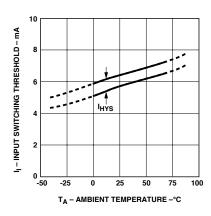

| Input Hysteresis<br>Current        | I <sub>HYS</sub> | 0.3  | 0.8   |           | mA    |                                                                     | 2          |      |

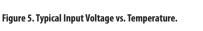

| Logic Low Output<br>Voltage        | V <sub>OL</sub>  |      |       | 0.5       | Volts | $I_{OL} = 6.4 \text{ mA}$ $I_{I} = 3 \text{ mA}$ (4 TTL Loads)      | 6          |      |

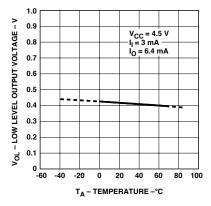

| Logic High Output<br>Voltage       | V <sub>OH</sub>  | 2.4  |       |           | Volts | $I_{OH} = -2.6 \text{ mA},  I_{I} = 12 \text{ mA}$                  | 7          |      |

| Output Leakage                     | I <sub>OHH</sub> |      |       | 100       | μΑ    | $V_0 = 5.5 \text{ V}$ $I_1 = 20 \text{ mA}$                         |            |      |

| Current $(V_{OUT} > V_{CC})$       |                  |      |       | 500       | μΑ    | $V_0 = 20 \text{ V}$ $V_{CC} = 4.5 \text{ V}$                       |            |      |

| Logic High Enable<br>Voltage       | $V_{EH}$         | 2.0  |       |           | Volts |                                                                     |            |      |

| Logic Low Enable<br>Voltage        | $V_{_{EL}}$      |      |       | 0.8       | Volts |                                                                     |            |      |

| Logic High Enable                  | I <sub>EH</sub>  |      |       | 20        | μΑ    | $V_E = 2.7 \text{ V}$                                               |            |      |

| Current                            |                  |      |       | 100       | μΑ    | $V_E = 5.5 \text{ V}$                                               |            |      |

|                                    |                  |      | 0.004 | 250       | μΑ    | $V_E = 20 \text{ V}$                                                |            |      |

| Logic Low Enable<br>Current        | I <sub>EL</sub>  |      |       | -0.32     | mA    | $V_E = 0.4 \text{ V}$                                               |            |      |

| Logic Low Supply                   | $I_{CCL}$        |      | 4.5   | 6.0       | mA    | $V_{CC} = 5.5 \text{ V}$ $I_{I} = 0 \text{ mA}$                     |            |      |

| Current                            |                  |      | 5.25  | 7.5       | mA    | $V_{CC} = 20 \text{ V}$ $V_E = \text{Don't Care}$                   |            |      |

| Logic High Supply                  | I <sub>CCH</sub> |      | 2.7   | 4.5       | mA    | $V_{cc} = 5.5 \text{ V}$ $I_i = 20 \text{ mA}$                      |            |      |

| Current                            |                  |      | 3.1   | 6.0       | mA    | $V_{cc} = 20 \text{ V}$ $V_E = Don't Care$                          |            |      |

| High Impedance                     | I <sub>OZL</sub> |      |       | -20       | μΑ    | $V_{o} = 0.4 \text{ V}$ $V_{E} = 2 \text{ V},$                      |            |      |

| State Output                       | OZH              |      |       | 20        | μΑ    | $V_0 = 2.4 \text{ V}$ $I_1 = 20 \text{ mA}$                         |            |      |

| Current                            |                  |      |       | 100       | μΑ    | $V_0 = 5.5 \text{ V}$                                               |            |      |

|                                    |                  |      |       | 500       | μΑ    | $V_{o} = 20 \text{ V}$                                              |            |      |

| Logic Low Short<br>Circuit Output  | l <sub>OSL</sub> | 25   |       |           | mA    | $V_0 = V_{CC} = 5.5 \text{ V}$ $I_1 = 0 \text{ mA}$                 |            | 5    |

| Current                            |                  | 40   |       |           | mA    | $V_0 = V_{CC} = 20 \text{ V}$ $I_1 = 0 \text{ mA}$                  |            | 5    |

| Logic High Short<br>Circuit Output | $I_{OSH}$        | -10  |       |           | mA    | $V_{CC} = 5.5 \text{ V}, I_{I} = 20 \text{ mA}, V_{O} = \text{GNE}$ | )          | 5    |

| Current                            |                  | -25  |       |           | mA    | $V_{CC} = 20 \text{ V}$ $I_{I} = 20 \text{ mA}$ , $V_{O} = GND$     | )          | 5    |

| Input Capacitance                  | C <sub>IN</sub>  |      | 120   |           | рF    | $f = 1 \text{ MHz}$ , $V_1 = 0 \text{ V dc}$ ,<br>Pins 1 and 2      |            |      |

## **Switching Specifications**

For  $0^{\circ}\text{C} \leq \text{T}_{A} \leq 70^{\circ}\text{C}$ ,  $4.5 \text{ V} \leq \text{V}_{CC} \leq 20 \text{ V}$ ,  $\text{V}_{E} = 0.8 \text{ V}$ , all typicals at  $\text{T}_{A} = 25^{\circ}\text{C}$  and  $\text{V}_{CC} = 5 \text{ V}$  unless otherwise noted. See note 13.

| Parameter                                                       | Symbol                             | Min.  | Тур.   | Max. | Units | Test Conditions                                                                            | Fig.          | Note |

|-----------------------------------------------------------------|------------------------------------|-------|--------|------|-------|--------------------------------------------------------------------------------------------|---------------|------|

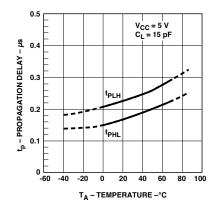

| Propagation Delay Time<br>to Logic High Output Level            | t <sub>PLH</sub>                   |       | 0.23   | 1.6  | μs    | $V_{E} = 0 \text{ V},$ $C_{L} = 15 \text{ pF}$                                             | 8, 9,<br>10   | 7    |

| Propagation Delay Time<br>to Logic Low Output Level             | t <sub>PHL</sub>                   |       | 0.17   | 1.0  | μs    | $V_{E} = 0 \text{ V},$ $C_{L} = 15 \text{ pF}$                                             | 8, 9,<br>10   | 8    |

| Propagation Delay Time<br>Skew                                  | t <sub>PLH</sub> -t <sub>PHL</sub> |       | 60     |      | ns    | $I_1 = 20 \text{ mA},$<br>$C_L = 15 \text{ pF}$                                            | 8, 9,<br>10   |      |

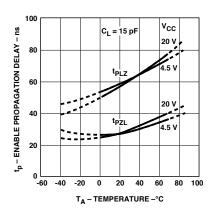

| Output Enable Time to<br>Logic Low Level                        | t <sub>PZL</sub>                   |       | 25     |      | ns    | $I_1 = 0 \text{ mA},$ $C_L = 15 \text{ pF}$                                                | 12, 13,<br>15 |      |

| Output Enable Time to<br>Logic High Level                       | t <sub>PZH</sub>                   |       | 28     |      | ns    | $I_1 = 20 \text{ mA},$<br>$C_L = 15 \text{ pF}$                                            | 12, 13,<br>14 |      |

| Output Disable Time to<br>Logic Low Level                       | t <sub>PLZ</sub>                   |       | 60     |      | ns    | $I_1 = 0 \text{ mA},$ $C_L = 15 \text{ pF}$                                                | 12, 13,<br>15 |      |

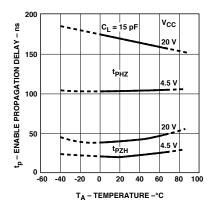

| Output Disable Time to<br>Logic High Level                      | t <sub>PHZ</sub>                   |       | 105    |      | ns    | $I_1 = 20 \text{ mA},$ $C_L = 15 \text{ pF}$                                               | 12, 13,<br>14 |      |

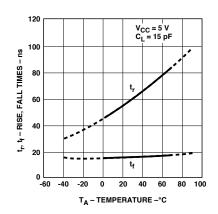

| Output Rise Time<br>(10-90%)                                    | t <sub>r</sub>                     |       | 55     |      | ns    | $V_{cc} = 5 \text{ V},$ $C_L = 15 \text{ pF}$                                              | 8, 9,<br>11   | 9    |

| Output Fall Time<br>(90-10%)                                    | t <sub>f</sub>                     |       | 15     |      | ns    | $V_{CC} = 5 \text{ V},$ $C_L = 15 \text{ pF}$                                              | 8, 9,<br>11   | 10   |

| Common Mode Transient<br>Immunity at Logic High<br>Output Level | CM <sub>H</sub>                    | 1,000 | 10,000 |      | V/µs  | $V_{CM} = 50 \text{ V (peak)}$<br>$I_{I} = 12 \text{ mA,}$<br>$T_{A} = 25^{\circ}\text{C}$ | 16            | 11   |

| Common Mode Transient<br>Immunity at Logic Low<br>Output Level  | CM <sub>L</sub>                    | 1,000 | 10,000 |      | V/µs  | $V_{CM} = 50 \text{ V (peak)}$<br>$I_1 = 3 \text{ mA},$<br>$T_A = 25^{\circ}\text{C}$      | 16            | 12   |

## **Package Characteristics**

For  $0^{\circ}\text{C} \leq \text{T}_{A} \leq 70^{\circ}\text{C}$ , unless otherwise specified. All typicals at  $\text{T}_{A} = 25^{\circ}\text{C}$ .

| A                                            |                  |      |      | A    |       |                                                    |      |       |

|----------------------------------------------|------------------|------|------|------|-------|----------------------------------------------------|------|-------|

| Parameter                                    | Symbol           | Min. | Тур. | Max. | Units | Test Conditions                                    | Fig. | Notes |

| Input-Output Momentary<br>Withstand Voltage* | $V_{\rm ISO}$    | 3750 |      |      | V rms | RH $\leq$ 50%, t = 1 min,<br>T <sub>A</sub> = 25°C |      | 6, 14 |

| Resistance, Input-Output                     | R <sub>I-O</sub> |      | 1012 |      | ohms  | V <sub>I-O</sub> = 500 V dc                        |      | 6     |

| Capacitance, Input-Output                    | C <sub>I-O</sub> |      | 1.0  |      | pF    | $f = 1 \text{ MHz}, V_{I-O} = 0 \text{ V}$         |      | 6     |

<sup>\*</sup>The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating refer to the IEC/EN/DIN EN 60747-5-2 Insulation Characteristics Table (if applicable), your equipment level safety specification, or Avago Application Note 1074, "Optocoupler Input-Output Endurance Voltage."

#### Notes:

- 1. ≤ 1  $\mu$ s pulse width, 300 pps.

- 2. Derate linearly above 70°C free air temperature at a rate of 1.6 mW/°C. Proper application of the derating factors will prevent IC junction temperatures from exceeding 125°C for ambient temperatures up to 85°C.

- 3. Derate linearly above 70°C free air temperature at a rate of 3.8 mW/°C.

- 4. Derate linearly above 70°C free air temperature at a rate of 4.6 mW/°C.

- 5. Duration of output short circuit time shall not exceed 10 ms.

- 6. The device is considered a two terminal device, pins 1, 2, 3, and 4 are connected together and pins 5, 6, 7, and 8 are connected together.

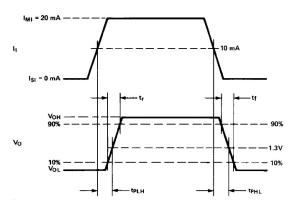

- 7. The t<sub>PLH</sub> propagation delay is measured from the 10 mA level on the leading edge of the input pulse to the 1.3 V level on the leading edge of the output pulse.

- 8. The t<sub>PHL</sub> propagation delay is measured from the 10 mA level on the trailing edge of the input pulse to the 1.3 V level on the trailing edge of the output pulse.

- 9. The rise time, t, is measured from the 10% to the 90% level on the rising edge of the output logic pulse.

- 10. The fall time,  $t_{\mu}$  is measured from the 90% to the 10% level on the falling edge of the output logic pulse.

- 11. Common mode transient immunity in the logic high level is the maximum (negative)  $dV_{CM}/dt$  on the trailing edge of the common mode pulse,  $V_{CM}$ , which can be sustained with the output voltage in the logic high state (i.e.,  $V_0 \ge 2 \text{ V}$ ).

- 12. Common mode transient immunity in the logic low level is the maximum (positive)  $dV_{CM}/dt$  on the leading edge of the common mode pulse,  $V_{CM}$ , which can be sustained with the output voltage in the logic low state (i.e.,  $V_{O} \le 0.8 \, \text{V}$ ).

- 13. Use of a 0.1  $\mu F$  bypass capacitor connected between pins 5 and 8 is recommended.

- 14. In accordance with UL 1577, each optocoupler momentary withstand is proof tested by applying an insulation test voltage  $\geq$  4500 V rms for 1 second (leakage detection current limit,  $I_{Lo} \leq 5 \mu A$ ).

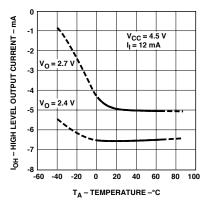

Figure 2. Typical Output Voltage vs. Loop Current.

Figure 3. Typical Current Switching Threshold vs. Temperature.

Figure 4. Typical Input Loop Voltage vs. Input Current.

Figure 6. Typical Logic Low Output Voltage vs. Temperature.

Figure 7. Typical Logic High Output Current vs. Temperature.

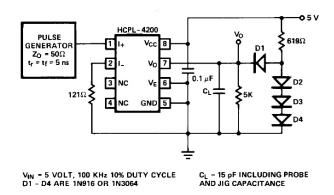

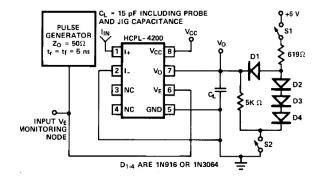

Figure 8. Test Circuit for  $\mathbf{t}_{_{\mathrm{PHL}}},\,\mathbf{t}_{_{\mathrm{PLH}}},\,\mathbf{t}_{_{\mathrm{r}}},\,\mathrm{and}\,\,\mathbf{t}_{_{\mathrm{r}}}.$

Figure 9. Waveforms for  $\mathbf{t}_{\text{PHL}}$ ,  $\mathbf{t}_{\text{PLH}}$ ,  $\mathbf{t}_{\text{r}}$ , and  $\mathbf{t}_{\text{f}}$ .

Figure 10. Typical Propagation Delay vs. Temperature.

Figure 11. Typical Rise, Fall Time vs. Temperature.

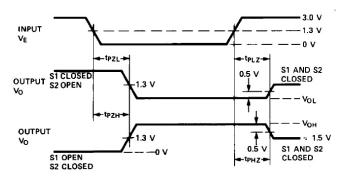

Figure 12. Test Circuit for  $\mathbf{t_{\rm PZH'}}\,\mathbf{t_{\rm PZL'}},\mathbf{t_{\rm PHZ'}}$  and  $\mathbf{t_{\rm PLZ}}.$

Figure 13. Waveforms for  $\mathbf{t}_{_{\mathrm{PZH}'}}\mathbf{t}_{_{\mathrm{PZL}'}}\mathbf{t}_{_{\mathrm{PHZ}'}}$  and  $\mathbf{t}_{_{\mathrm{PLZ}}}$ .

Figure 14. Typical Logic High Enable Propagation Delay vs. Temperature.

Figure 15. Typical Logic Low Enable Propagation Delay vs. Temperature.

Figure 16. Test Circuit for Common Mode Transient Immunity.

#### **Applications**

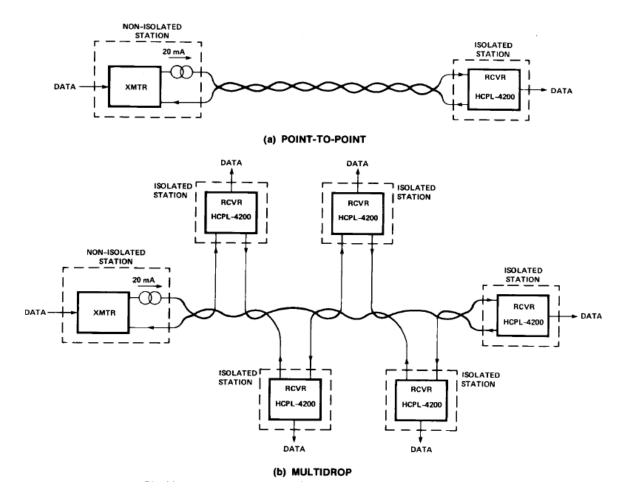

Data transfer between equipment which employs current loop circuits can be accomplished via one of three configurations: simplex, half duplex or full duplex communication. With these configurations, point-to-point and multidrop arrangements are possible. The appropriate configuration to use depends upon data rate, number of stations, number and length of lines, direction of data flow, protocol, current source location and voltage compliance value, etc.

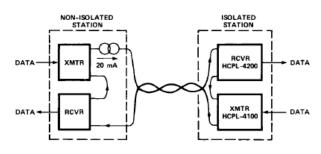

#### Simplex

The simplex configuration, whether point to point or multidrop, gives unidirectional data flow from transmitter to receiver(s). This is the simplest configuration for use in long line length (two wire), for high data rate, and low current source compliance level applications. Block diagrams of simplex point-to-point and multidrop arrangements are given in Figures 17a and 17b respectively for the HCPL-4200 receiver optocoupler.

For the highest data rate performance in a current loop, the configuration of a non-isolated active transmitter (containing current source) transmitting data to a remote isolated receiver(s) should be used. When the current source is located at the transmitter end, the loop is charged approximately to  $V_{\text{MI}}$  (2.5 V). Alternatively, when the current source is located at the receiver end, the loop is charged to the full compliance voltage level. The lower the charged voltage level the faster the data rate will be. In the configurations of Figures 17a and 17b, data rate is independent of the current source voltage compliance level. An adequate compliance level of current source must be available for voltage drops across station(s) during the MARK state in multidrop applications or for long line length. The maximum compliance level is determined by the transmitter breakdown characteristic.

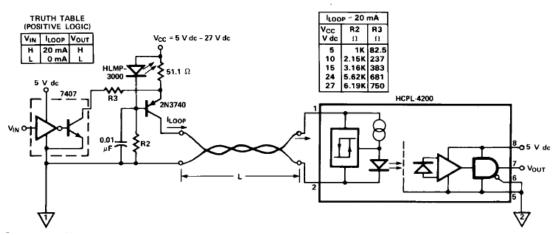

A recommended non-isolated active transmitter circuit which can be used with the HCPL-4200 in point-to-point or in multidrop 20 mA current loop applications is given in Figure 18. The current source is controlled via a standard TTL 7407 buffer to provide high output impedance of current source in both the ON

Figure 17. Simplex Current Loop System Configurations for (a) Point-to-Point, (b) Multidrop.

and OFF states. This non-isolated active transmitter provides a nominal 20 mA loop current for the listed values of  $V_{\rm CC'}$  R2 and R3 in Figure 18.

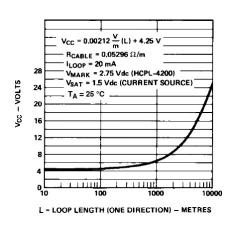

Length of current loop (one direction) versus minimum required DC supply voltage,  $V_{cc'}$  of the circuit in Figure 18 is graphically illustrated in Figure 19. Multidrop configurations will require larger  $V_{cc}$  than Figure 19 predicts in order to account for additional station terminal voltage drops.

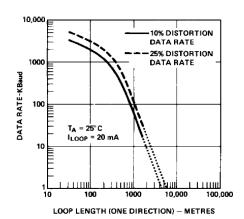

Typical data rate performance versus distance is illustrated in Figure 20 for the combination of a non-isolated active transmitter and HCPL-4200 optically coupled current loop receiver shown in Figure 18. Curves are shown for 10% and 25% distortion data rate. 10% (25%) distortion data rate is defined as that rate at which 10% (25%) distortion occurs to output bit interval with respect to input bit interval. An input Non-Return-to-Zero (NRZ)

test waveform of 16 bits (00000010111111101) was used for data rate distortion measurements. Data rate is independent of current source supply voltage,  $V_{\rm cc}$ .

The cable used contained five pairs of unshielded, twisted, 22 AWG wire (Dearborn #862205). Loop current is 20 mA nominal. Input and output logic supply voltages are 5 V dc.

#### **Full Duplex**

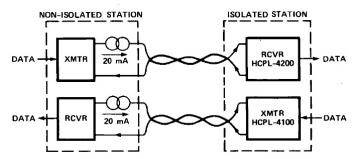

The full duplex point-to-point communication of Figure 21 uses a four wire system to provide simultaneous, bidirectional data communication between local and remote equipment. The basic application uses two simplex point-to-point loops which have two separate, active, non-isolated units at one common end of the loops. The other end of each loop is isolated.

As Figure 21 illustrates, the combination of Avago current loop optocouplers, HCPL-4100 transmitter and HCPL-4200

Figure 18. Recommended Non-Isolated Active Transmitter with HCPL-4200 Isolated Receiver for Simplex Point-to-Point 20 mA Current Loop.

receiver, can be used at the isolated end of current loops. Cross talk and common mode coupling are greatly reduced when optical isolation is implemented at the same end of both loops, as shown. The full duplex data rate is limited by the non-isolated active receiver current loop. Comments mentioned under simplex configuration apply to the full duplex case. Consult the HCPL-4100 transmitter optocoupler data sheet for specified device performance.

#### **Half Duplex**

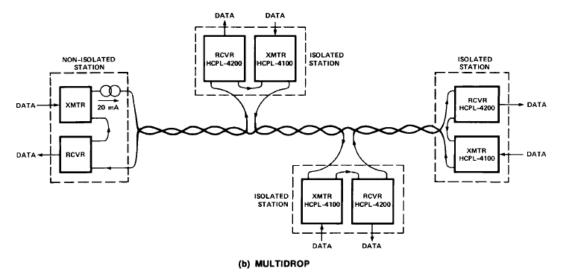

The half duplex configuration, whether point-to-point or multidrop, gives non-simultaneous bidirectional data flow from transmitters to receivers shown in Figures 22a and 22b. This configuration allows the use of two wires to carry data back and forth between local and remote

units. However, protocol must be used to determine which specific transmitter can operate at any given time. Maximum data rate for a half duplex system is limited by the loop current charging time. These considerations were explained in the Simplex configuration section.

Figures 22a and 22b illustrate half duplex application for the combination of HCPL-4100/-4200 optocouplers. The unique and complementary designs of the HCPL-4100 transmitter and HCPL-4200 receiver optocouplers provide many designed-in benefits. For example, total optical isolation at one end of the current loop is easily accomplished, which results in substantial removal of common mode influences, elimination of ground potential

Figure 19. Minimum Required Supply Voltage,  $\mathbf{V}_{cc'}$  vs. Loop Length for Current Loop Circuit of Figure 19.

Figure 20. Typical Data Rate vs. Distance.

differences and reduction of power supply requirements. With this combination of HCPL-4100/-4200 optocouplers, specific current loop noise immunity is provided, i.e., minimum SPACE state current noise immunity is 1 mA, MARK state noise immunity is 8 mA.

Voltage compliance of the current source must be of an adequate level for operating all units in the loop while not exceeding 27 V dc, the maximum breakdown voltage for the HCPL-4100. Note that the HCPL-4100 transmitter will allow loop current to conduct when input  $V_{CC}$  power is off. Consult the HCPL-4100 transmitter optocoupler data sheet for specified device performance.

For more information about the HCPL-4100/-4200 optocouplers, consult Application Note 1018.

Figure 21. Full Duplex Point-to-Point Current Loop System Configuration.

#### (a) POINT-TO-POINT

Figure~22.~Half~Duplex~Current~Loop~System~Configurations~for~(a)~Point-to-Point,~(b)~Multidrop.

For product information and a complete list of distributors, please go to our website: **www.avagotech.com**

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies Limited in the United States and other countries. Data subject to change. Copyright © 2007 Avago Technologies Limited. All rights reserved. Obsoletes 5989-2100EN AV01-0541EN July 30, 2007