# LOGIC-INPUT CMOS QUAD DRIVERS

#### **FEATURES**

| High Peak Output Current           | 1.2A |

|------------------------------------|------|

| Wide Operating Range               |      |

| Symmetrical Rise and Fall Times    |      |

| Short, Equal Delay Times           |      |

| Latchproof! Withstands 500mA Induc |      |

| 3 Input Logic Choices              |      |

| — AND/NAND/AND+Inv                 |      |

| 2kV ESD Protection on All Pins     |      |

#### **APPLICATIONS**

- General-Purpose CMOS Logic Buffer

- Driving All Four MOSFETs in an H-Bridge

- **■** Direct Small Motor Driver

- Relay or Peripheral Drivers

- CCD Driver

- **■** Pin-Switching Network Driver

#### **GENERAL DESCRIPTION**

The TC446X family of four-output CMOS buffer/drivers are an expansion from our earlier single- and dual-output drivers. Each driver has been equipped with a two-input logic gate for added flexibility.

The TC446X drivers can source up to 250 mA into loads referenced to ground. Heavily loaded clock lines, coaxial cables, and piezoelectric transducers can all be easily driven with the 446X series drivers. The only limitation on loading is that total power dissipation in the IC must be kept within the power dissipation limits of the package.

The TC446X series will not latch under any conditions within their power and voltage ratings. They are not subject to damage when up to 5V of noise spiking (either polarity) occurs on the ground line. They can accept up to half an amp of inductive kickback current (either polarity) into their outputs without damage or logic upset. In addition, all terminals are protected against ESD to at least 2000V.

#### ORDERING INFORMATION

| Part No.  | Package            | Temp. Range     |

|-----------|--------------------|-----------------|

| TC446*COE | 16-Pin SOIC (Wide) | 0° to +70°C     |

| TC446*CPD | 14-Pin Plastic DIP | 0° to +70°C     |

| TC446*EJD | 14-Pin CerDIP      | – 40° to +85°C  |

| TC446*MJD | 14-Pin CerDIP      | – 55° to +125°C |

\*A digit must be added in this position to define the device input configuration: TC446X - 7 NAND

8 AND

9 AND with INV

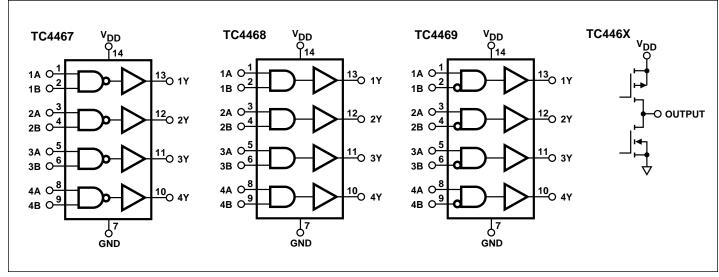

#### LOGIC DIAGRAMS

TC4467 TC4468 TC4469

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage(GND – 5V)                          |                  |

|---------------------------------------------------|------------------|

| Maximum Chip Temperature                          |                  |

| Operating                                         | +150°C           |

| Storage                                           | − 65° to +150°C  |

| Maximum Lead Temperature                          |                  |

| (Soldering, 10 sec)                               | +300°C           |

| Operating Ambient Temperature Range               |                  |

| C Device                                          |                  |

| E Device                                          | . − 40° to +85°C |

| M Device                                          | − 55° to +125°C  |

| Package Power Dissipation (T <sub>A</sub> ≤ 70°C) |                  |

| 14-Pin CerDIP                                     | 840mW            |

| 14-Pin Plastic DIP                                | 800mW            |

| 16-Pin Wide SOIC                                  |                  |

|                                                   |                  |

| Package Thermal Resis | stance             |         |

|-----------------------|--------------------|---------|

| 14-Pin CerDIP         | R <sub>0J-A</sub>  | 100°C/W |

|                       | R <sub>θ</sub> J-C | 23°C/W  |

| 14-Pin Plastic DIP    | R <sub>θ,J-A</sub> | 80°C/W  |

|                       | R <sub>θ</sub> J-C | 35°C/W  |

16-Pin Wide SOIC  $R_{\theta J\text{-}A}$  ......95°C/W

\*Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied.

Exposure to Absolute Maximum Rating Conditions for extended periods

**ELECTRICAL CHARACTERISTICS:** Measured at  $T_A = +25^{\circ}C$  with  $4.5V \le V_{DD} \le 18V$ , unless otherwise specified.

may affect device reliability.

| Symbol              | Parameter                                     | Test Conditions                                | Min                     | Тур | Max             | Unit |

|---------------------|-----------------------------------------------|------------------------------------------------|-------------------------|-----|-----------------|------|

| Input               |                                               |                                                |                         |     |                 |      |

| V <sub>IH</sub>     | Logic 1, High Input Voltage                   | Note 3                                         | 2.4                     |     | V <sub>DD</sub> | V    |

| V <sub>IL</sub>     | Logic 0, Low Input Voltage                    | Note 3                                         | 0                       |     | 0.8             | V    |

| I <sub>IN</sub>     | Input Current                                 | $0V \le V_{IN} \le V_{DD}$                     | <b>–</b> 1              |     | 1               | μΑ   |

| Output              |                                               |                                                |                         |     | •               | •    |

| V <sub>OH</sub>     | High Output Voltage                           | I <sub>LOAD</sub> = 100μA (Note 1)             | V <sub>DD</sub> - 0.025 |     |                 | V    |

| $\overline{V_{OL}}$ | Low Output Voltage                            | I <sub>LOAD</sub> = 10mA (Note 1)              |                         |     | 0.15            | V    |

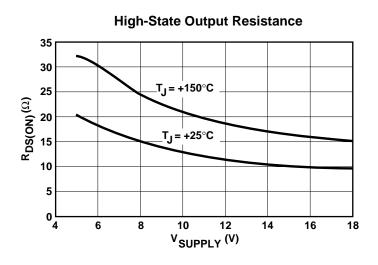

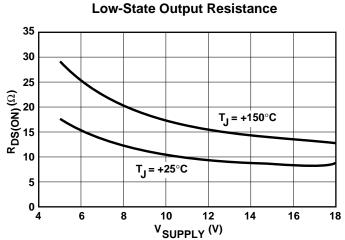

| $\overline{R_0}$    | Output Resistance                             | I <sub>OUT</sub> = 10mA, V <sub>DD</sub> = 18V |                         | 10  | 15              | Ω    |

| I <sub>PK</sub>     | Peak Output Current                           |                                                |                         | 1.2 |                 | Α    |

| I <sub>DC</sub>     | Continuous Output Current                     | Single Output<br>Total Package                 |                         |     | 300<br>500      | mA   |

| I                   | Latch-Up Protection Withstand Reverse Current | $4.5V \le V_{DD} \le 16V$                      | 500                     |     |                 | mA   |

| Switching           | Time                                          |                                                | <u>'</u>                |     |                 | 1    |

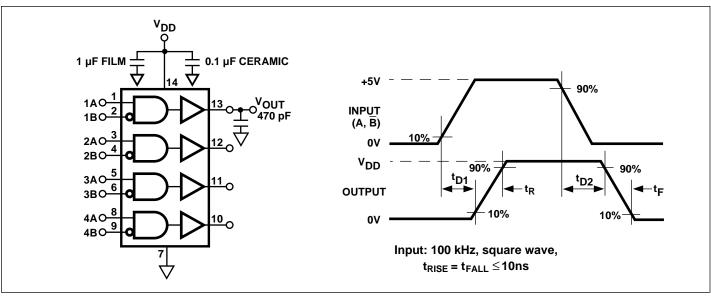

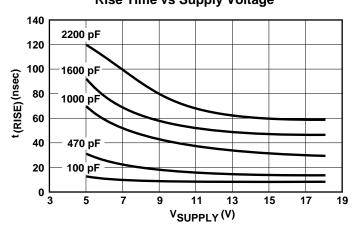

| $\overline{t_R}$    | Rise Time                                     | Figure 1                                       |                         | 15  | 25              | nsec |

| $t_{F}$             | Fall Time                                     | Figure 1                                       |                         | 15  | 25              | nsec |

| t <sub>D1</sub>     | Delay Time                                    | Figure 1                                       |                         | 40  | 75              | nsec |

| t <sub>D2</sub>     | Delay Time                                    | Figure 1                                       |                         | 40  | 75              | nsec |

| Power Sup           | pply                                          |                                                |                         |     |                 | •    |

| Is                  | Power Supply Current                          |                                                |                         | 1.5 | 4               | mA   |

| $V_{DD}$            | Power Supply Voltage                          | Note 2                                         | 4.5                     |     | 18              | V    |

#### **TRUTH TABLE**

| Part No.       |   | TC4467 | NANE | ) | 7 | C446 | B AND | ١ | TC | TC4469 AND/INV |   |   |  |

|----------------|---|--------|------|---|---|------|-------|---|----|----------------|---|---|--|

| INPUTS A       | Н | Н      | L    | L | Н | Н    | L     | L | Н  | Н              | L | L |  |

| INPUTS B       | Н | L      | Н    | L | Н | L    | Н     | L | Н  | L              | Н | L |  |

| OUTPUTS TC446X | L | Н      | Н    | Н | Н | L    | L     | L | L  | Н              | L | L |  |

**ELECTRICAL CHARACTERISTICS:** Measured throughout operating temperature range with  $4.5V \le V_{DD} \le 18V$ , unless otherwise specified.

| Symbol              | Parameter                                     | Test Conditions                                 | Min                     | Тур | Max  | Unit |

|---------------------|-----------------------------------------------|-------------------------------------------------|-------------------------|-----|------|------|

| Input               |                                               |                                                 | '                       | '   | 1    |      |

| $\overline{V_{IH}}$ | Logic 1, High Input Voltage                   | (Note 3)                                        | 2.4                     |     |      | V    |

| $\overline{V_{IL}}$ | Logic 0, Low Input Voltage                    | (Note 3)                                        |                         |     | 0.8  | V    |

| I <sub>IN</sub>     | Input Current                                 | $0V \le V_{IN} \le V_{DD}$                      | - 10                    |     | 10   | μΑ   |

| Output              |                                               |                                                 |                         |     |      | -    |

| V <sub>OH</sub>     | High Output Voltage                           | I <sub>LOAD</sub> = 100 μA (Note 1)             | V <sub>DD</sub> - 0.025 |     |      | V    |

| $V_{OL}$            | Low Output Voltage                            | I <sub>LOAD</sub> = 10 mA (Note 1)              |                         |     | 0.30 | V    |

| Ro                  | Output Resistance                             | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 18V |                         | 20  | 30   | Ω    |

| I <sub>PK</sub>     | Peak Output Current                           |                                                 |                         | 1.2 |      | Α    |

| I                   | Latch-Up Protection Withstand Reverse Current | $4.5V \le V_{DD} \le 16V$                       | 500                     |     |      | mA   |

| Switching           | Time                                          |                                                 |                         |     |      |      |

| $\overline{t_R}$    | Rise Time                                     | Figure 1                                        |                         |     | 50   | nsec |

| t <sub>F</sub>      | Fall Time                                     | Figure 1                                        |                         |     | 50   | nsec |

| t <sub>D1</sub>     | Delay Time                                    | Figure 1                                        |                         |     | 100  | nsec |

| t <sub>D2</sub>     | Delay Time                                    | Figure 1                                        |                         |     | 100  | nsec |

| Power Sup           | pply                                          |                                                 | •                       | •   | •    | -    |

| Is                  | Power Supply Current                          |                                                 |                         |     | 8    | mA   |

| Is                  | Power Supply Voltage                          | Note 2                                          | 4.5                     |     | 18   | V    |

- **NOTES:** 1. Totem-pole outputs should not be paralleled because the propagation delay differences from one to the other could cause one driver to drive high a few nanoseconds before another. The resulting current spike, although short, may decrease the life of the device.

- 2. When driving all four outputs simultaneously in the same direction, V<sub>DD</sub> shall be limited to 16V. This reduces the chance that internal dv/dt will cause high-power dissipation in the device.

- 3. The input threshold has about 50 mV of hysteresis centered at approximately 1.5V. Slow moving inputs will force the device to dissipate high peak currents as the input transitions through this band. Input rise times should be kept below 5 µs to avoid high internal peak currents during input transitions. Static input levels should also be maintained above the maximum or below the minimum input levels specified in the "Electrical Characteristics" to avoid increased power dissipation in the device.

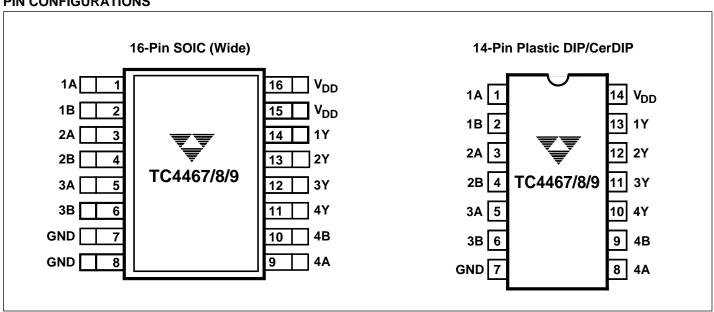

#### **PIN CONFIGURATIONS**

TC4467 TC4468 TC4469

# **Supply Bypassing**

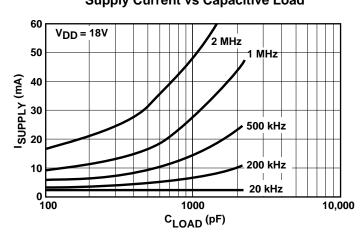

Large currents are required to charge and discharge large capacitive loads quickly. For example, charging a 1000 pF load to 18V in 25 ns requires 0.72A from the device's power supply.

To guarantee low supply impedance over a wide frequency range, a 1  $\mu F$  film capacitor in parallel with one or two low-inductance 0.1  $\mu F$  ceramic disk capacitors with short lead lengths (<0.5 in.) normally provide adequate bypassing.

### Grounding

The TC4467 and TC4469 contain inverting drivers. Potential drops developed in common ground impedances from input to output will appear as negative feedback and degrade switching speed characteristics. Instead, individual ground returns for input and output circuits, or a ground plane, should be used.

# **Input Stage**

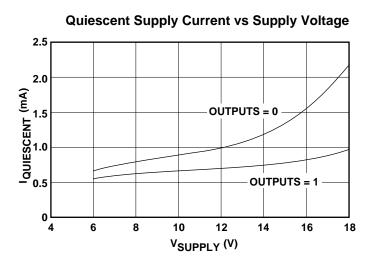

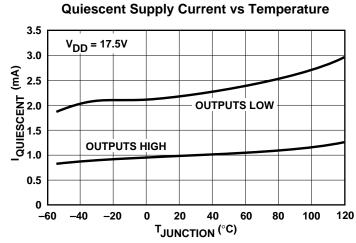

The input voltage level changes the no-load or quiescent supply current. The N-channel MOSFET input stage transistor drives a 2.5 mA current source load. With logic "0" outputs, maximum quiescent supply current is 4 mA. Logic "1" output level signals reduce quiescent current to 1.4 mA maximum. Unused driver inputs must be connected to  $V_{DD}$  or  $V_{SS}.$  Minimum power dissipation occurs for logic "1" outputs.

The drivers are designed with 50 mV of hysteresis. This provides clean transitions and minimizes output stage current spiking when changing states. Input voltage thresholds are approximately 1.5V, making any voltage greater than 1.5V up to  $V_{\rm DD}$  a logic 1 input . Input current is less than 1  $\mu A$  over this range.

# **Power Dissipation**

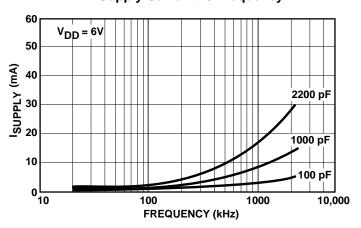

The supply current versus frequency and supply current versus capacitive load characteristic curves will aid in determining power dissipation calculations. TelCom Semiconductor's CMOS drivers have greatly reduced quiescent DC power consumption.

Input signal duty cycle, power supply voltage and load type, influence package power dissipation. Given power dissipation and package thermal resistance, the maximum ambient operating temperature is easily calculated. The 14-pin plastic package junction-to-ambient thermal resistance is 83.3°C/W. At +70°C, the package is rated at 800mW maximum dissipation. Maximum allowable chip temperature is +150°C.

Three components make up total package power dissipation:

- (1) Load-caused dissipation (P<sub>L</sub>)

- (2) Quiescent power (PQ)

- (3) Transition power (P<sub>T</sub>).

A capacitive-load-caused dissipation (driving MOSFET gates), is a direct function of frequency, capacitive load, and supply voltage. The power dissipation is:

$$P_L = f C V_S^2$$

,

where: f = Switching frequency C = Capacitive load V<sub>S</sub> = Supply voltage.

A resistive-load-caused dissipation for ground-referenced loads is a function of duty cycle, load current, and load voltage. The power dissipation is:

$$P_L = D (V_S - V_L) I_L$$

where: D = Duty cycle  $V_S = Supply voltage$   $V_L = Load voltage$  $I_L = Load current$ .

A resistive-load-caused dissipation for supply-referenced loads is a function of duty cycle, load current, and output voltage. The power dissipation is:

$$P_L = D V_O I_L$$

where: f = Switching frequency  $V_O = Device output voltage$  $I_L = Load current.$

Quiescent power dissipation depends on input signal duty cycle. Logic HIGH outputs result in a lower power dissipation mode, with only 0.6 mA total current drain (all devices driven). Logic LOW outputs raise the current to 4 mA maximum. The quiescent power dissipation is:

$$P_Q = V_S (D(I_H) + (1-D)I_L),$$

where:  $I_H =$  Quiescent current with all outputs LOW (4 mA max)

I<sub>L</sub> = Quiescent current with all outputs HIGH (0.6 mA max)

D = Duty cycle $V_S = Supply voltage.$  Transition power dissipation arises in the complementary configuration (TC446X) because the output stage N-channel and P-channel MOS transistors are ON simultaneously for a very short period when the output changes. The transition power dissipation is approximately:

$$P_T = f V_S (10 \times 10^{-9}).$$

Package power dissipation is the sum of load, quiescent and transition power dissipations. An example shows the relative magnitude for each term:

C = 1000 pF capacitive load

$V_S = 15V$

D = 50%

f = 200 kHz

$P_D$  = Package Power Dissipation =  $P_L + P_Q + P_T$

= 45 mW + 35 mW + 30 mW = 110 mW.

Maximum operating temperature:

$$T_{J} - \theta_{JA} (P_{D}) = 141^{\circ}C,$$

where:  $T_J$  = Maximum allowable junction temperature

(+150°C)

$\theta_{JA}$  = Junction-to-ambient thermal resistance (83.3°C/W) 14-pin plastic package.

**NOTE:** Ambient operating temperature should not exceed +85°C for "EJD" device or +125°C for "MJD" device.

Figure 1. Switching Time Test Circuit

TC4467 TC4468 TC4469

### **CHARACTERISTICS CURVES**

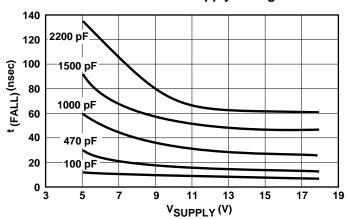

Rise Time vs Supply Voltage

Fall Time vs Supply Voltage

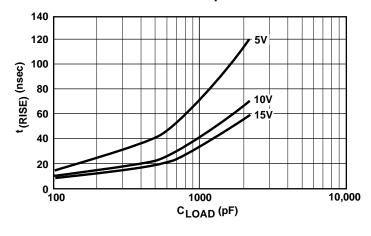

**Rise Time vs Capacitive Load**

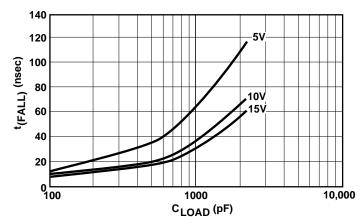

**Fall Time vs Capacitive Load**

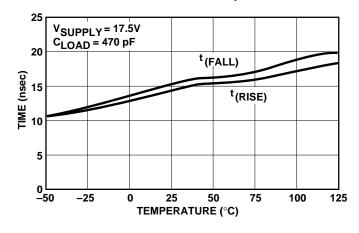

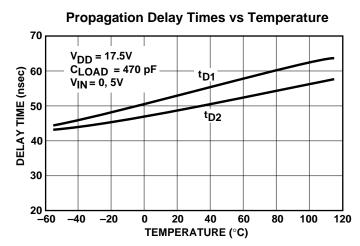

**Rise/Fall Times vs Temperature**

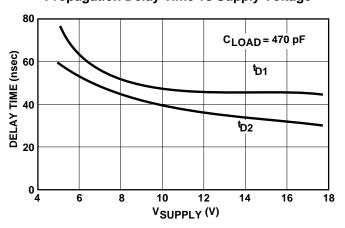

**Propagation Delay Time vs Supply Voltage**

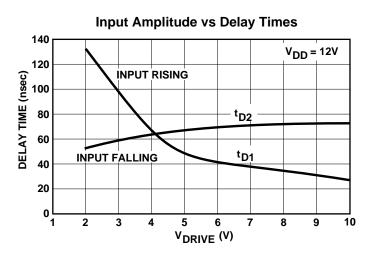

# **CHARACTERISTICS CURVES** (Cont.)

TC4467 TC4468 TC4469

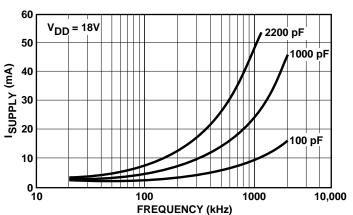

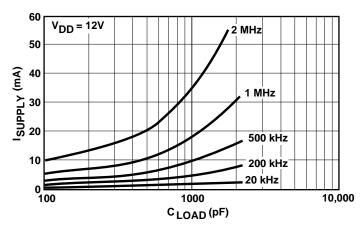

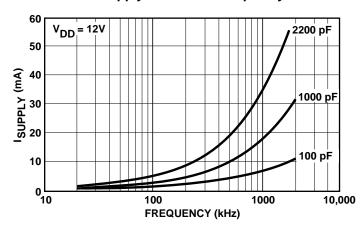

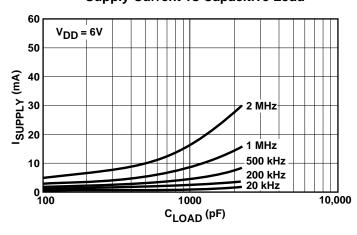

# **SUPPLY CURRENT CHARACTERISTICS** (Load on Single Output Only)

# Supply Current vs Capacitive Load

# Supply Current vs Frequency

### **Supply Current vs Capacitive Load**

### **Supply Current vs Frequency**

### **Supply Current vs Capacitive Load**

### **Supply Current vs Frequency**

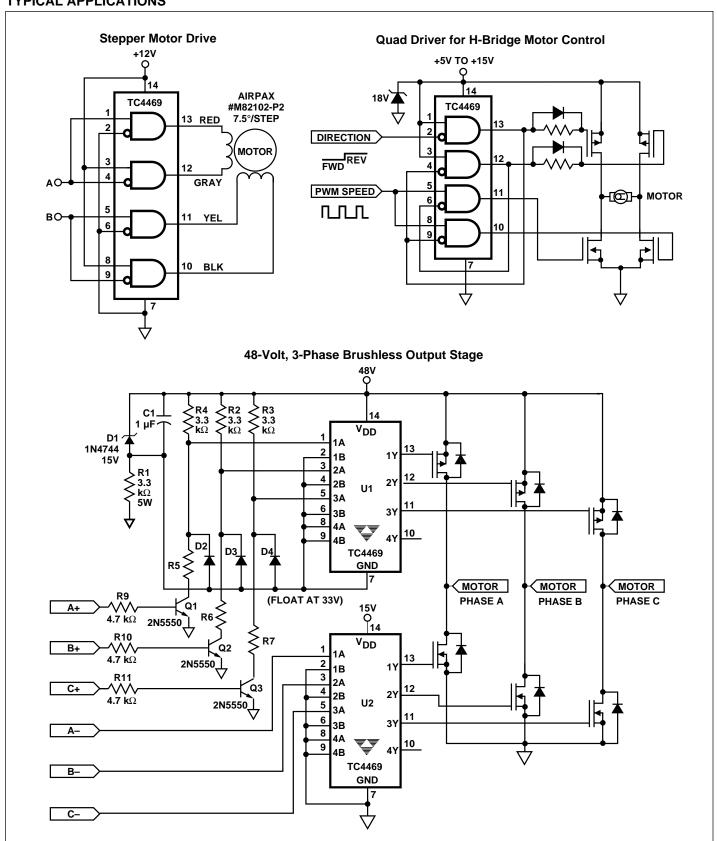

#### TYPICAL APPLICATIONS

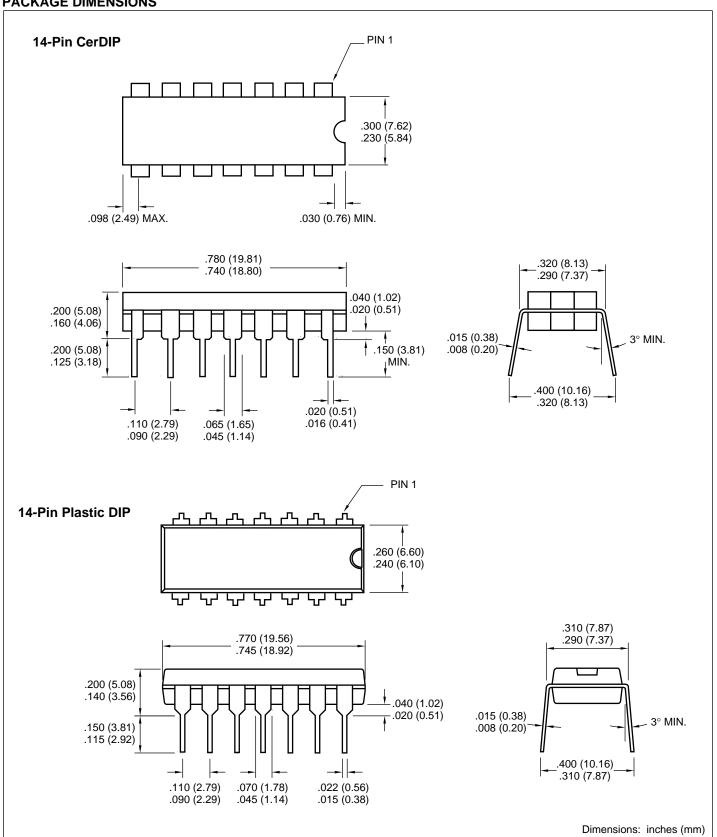

### **PACKAGE DIMENSIONS**

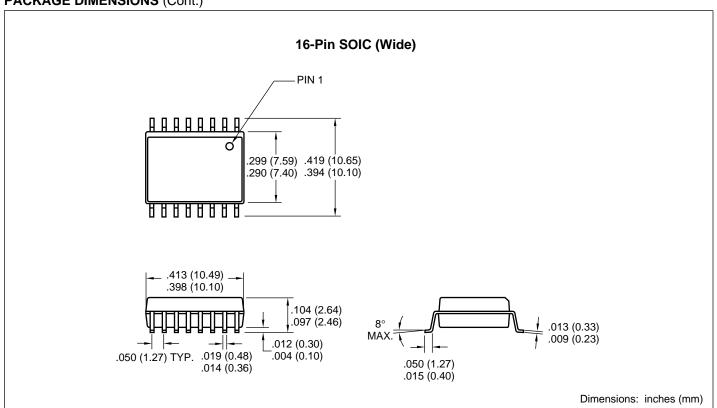

### PACKAGE DIMENSIONS (Cont.)

#### **Sales Offices**

**TelCom Semiconductor** 1300 Terra Bella Avenue P.O. Box 7267 Mountain View, CA 94039-7267 TEL: 415-968-9241

FAX: 415-967-1590

E-Mail: liter@c2smtp.telcom-semi.com

**TelCom Semiconductor Austin Product Center**

9101 Burnet Rd. Suite 214 Austin, TX 78758 TEL: 512-873-7100 FAX: 512-873-8236

TelCom Semiconductor H.K. Ltd. 10 Sam Chuk Street, Ground Floor San Po Kong, Kowloon Hong Kong TEL: 852-2324-0122 FAX: 852-2354-9957