June 2016 Rev. 1.0.1

## **GENERAL DESCRIPTION**

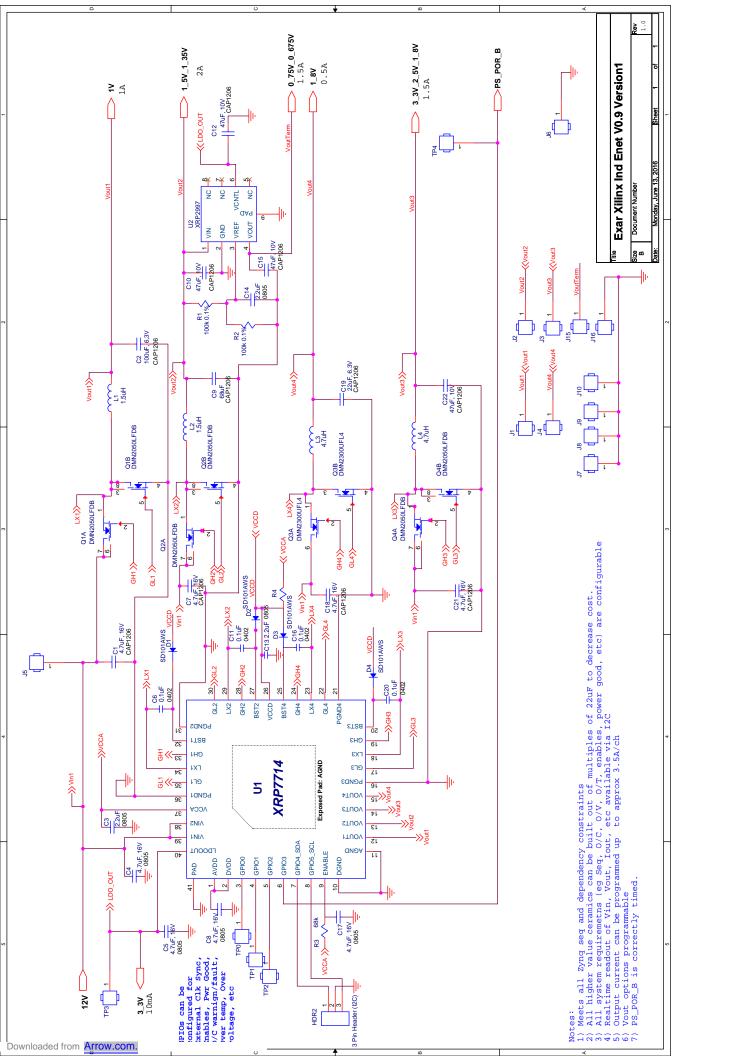

This reference design is a complete five-output power system designed to power a Xilinx Zynq-7020 All Programmable (AP) SoC and associated DDR3 memory in Industrial Ethernet applications. This reference design is focused on Industrial Ethernet applications leveraging HMS's Anybus IP on Xilinx. Although the power requirements of the core system building blocks remain relatively constant, the flexibility of Exar's Universal PMICs provides a power solution that can power the wider system requirements, whether a motor control board or human interface module.

The power system provides  $V_{\text{CCPINT}}$ ,  $V_{\text{CCINT}}$  and  $V_{\text{CCBRAM}}$  1.00V,  $V_{\text{CCO\_DDR}}$  programmable to 1.2/1.35/1.5V,  $V_{\text{TT}}$  0.60/0.675/0.75V,  $V_{\text{CCAUX}}$  and  $V_{\text{CCADC}}$  1.8V and  $V_{\text{CCO}}$  programmable from 1.8V to 3.3V. The entire power system fits in less than one square inch. The order and ramp rates for each supply are programmed to accommodate Zynq-7020 sequencing requirements. All power supply operations can be controlled over an I²C interface. Faults, output voltages and currents can also be monitored. 4 GPIO signals are available and can be programmed to provide the status of power good signals, enables, and faults. The board is supported by PowerArchitect<sup>TM</sup> 4.x and connects to the Exar Communications Module (XR77XXEVB-XCM-V80).

## **FEATURES**

## Xilinx Zynq-7020 All Programmable SoC Power System

- 4 Channel Power System using XRP7714

Programmable Digital PWM Switching

Controller

- VCCPINT, VCCINT and VCCBRAM 1.0V

- V<sub>CCO\_DDR</sub> programmable to 1.2/1.35/1.5V

- $V_{TT} 0.60/0.675/0.75V$

- V<sub>CCO</sub> programmable to from 1.8V to 3.3V

- VCCAUX and VCCADC 1.8V

#### I<sup>2</sup>C Interface

- Programming

- Monitoring

- Control

## **ZYNQ-7020 AP SOC POWER SOLUTION**

The Zynq-7020 AP SoC power reference design provides 4 output voltages. The order and ramp rates for each output are programmed to accommodate Zynq-7020 AP SoC sequencing requirements.

The power system was designed to operate at 650kHz as a good trade-off between space and efficiency.

## **Output 1/Channel 1 Configuration**

Channel 1 is designed to provide 1V to  $V_{\text{CCINT}}$ ,  $V_{\text{CCBRAM}}$  and  $V_{\text{CCPINT}}$  Zynq-7020 AP SoC rails at 2.0A. However, the hardware is capable of supporting output currents up to 3Amps.

#### **Output 2/Channel 2 Configuration**

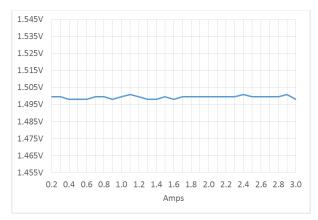

Channel 2 provides 1.5V to the DDR3 SDRAM subsystem as well as the DDR3 block inside the Zynq-7020 AP SoC. In addition, it sources the XRP2997 DDR Bus Termination Regulator which provides termination voltage for the DDR3 SDRAM signals. The channel is configured for a 2.0A output, but the hardware is capable of supporting up to a 3Amp load.

## **Output 3/Channel 3 Configuration**

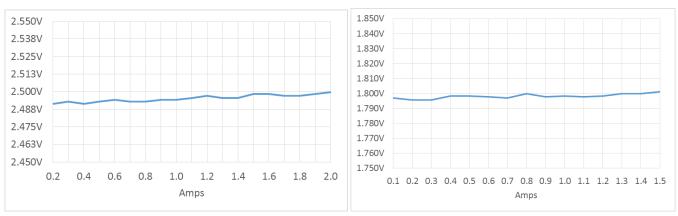

Channel 3 provides 2.5V to Zynq-7020 AP SoC IO banks ( $V_{\text{CCO}}$ ) and peripherals in the system. The channel is configured for a 1.5A output, but the hardware is capable of supporting up to a 2Amp load.

#### **Output 4/Channel 4 Configuration**

Channel 4 is designed to provide 1.8V to  $V_{\text{CCAUX}}$  and  $V_{\text{CCADC}}$  Zynq-7020 AP SoC rails at 0.5A. The channel is configured for a 0.5A output, but the hardware is capable of supporting up to a 1.5Amp load.

© 2016 Exar Corporation 2/14 Rev. 1.0.1

#### **LDOOUT**

LDOOUT is routed to XRP2997 control pin enabling the device.

## **CHANNEL SEQUENCING**

The XRP7714 sequencing has been designed to meet the Zynq-7020 AP SoC power up sequencing requirements.

## **Power-On Sequencing**

- **1. 1.0V** supply with 0.077V/msec ramp rate

- 2. 1.8V supply with 0.12V/msec ramp rate

- **3. 1.5V and 2.5V supplies** the 1.5V supply with 0.115V/msec ramp rate reaching the target level at the same time as the 2.5V supply with 0.192V/msec ramp rate.

## **Power-Down Sequencing**

- 1. 1.5V and 2.5V supplies the 1.5V supply following 0.1875V/msec ramp down rate; the 2.5V supply following 0.3125V/msec ramp down rate. Both channels regulate down to the shutdown threshold of 100mV before switching stops.

- 2. 1.0V and 1.8V supplies the 1.0V supply following 0.125V/msec ramp down rate; the 1.8V supply following 0.225V/msec ramp down rate. Both channels regulate down to the shutdown threshold of 100mV before switching stops.

© 2016 Exar Corporation 3/14 Rev. 1.0.1

## **ZYNQ-7020 AP SoC POWER ON RESET**

XRP7714 will generate a power on reset signal on GPIO3 to the Zynq-7020 AP SoC 400ms after the last rail is in regulation.

## **POWERING UP THE BOARD**

The board hardware is provided capable of supporting an input voltage range of 5.5V to 15V with power connected directly to J5 (VIN) and J6 (GND).

#### I<sup>2</sup>C Interface

The Zynq-7020 AP SoC power reference design schematic shows an  $I^2C$  interface connector (HDR2) to connect the Exar Communications Module (XR77XXEVB-XCM-V80 which has its own users guide available). This provides an interface with PowerArchitect<sup>TM</sup> 4.x allowing programming of the board.

Ensure the XCM is configured to use the on board pull-up resistors (check jumper settings).

If communication between Zynq-7020 AP SoC and XRP7714 is desired, ensure that the Zynq-7020 AP SoC system board has pull-up resistors installed.

For more information how to implement power subsystem control and monitoring via  $I^2C$  bus refer to ANP-31.

## **Configuring the Board**

The board is typically delivered with a XRP7714 which has not yet had its OTP memory burned with a specific configuration. This allows the user to select a different VIO voltage or DDR memory voltage than the one used in the default configuration file available from Exar's web site.

https://www.exar.com/products/zyng-7020

#### TYPICAL PERFORMANCE CHARACTERISTICS

All data taken at  $V_{IN} = 12V$ ,  $f_{SW}=650kHz$ ,  $T_J = T_A = 25$ °C, unless otherwise specified

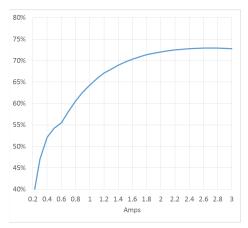

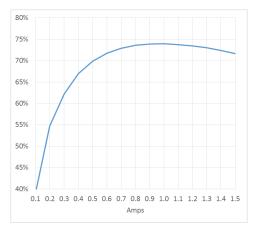

Fig. 1: Channel 1, 1.0V Efficiency

Fig. 3: Channel 3, 2.5V Efficiency

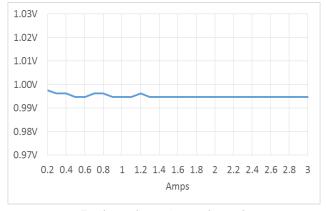

Fig. 5: Channel 1, 1.0V Load Regulation

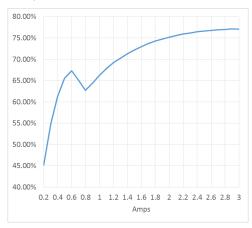

Fig. 2: Channel 2, 1.5V Efficiency

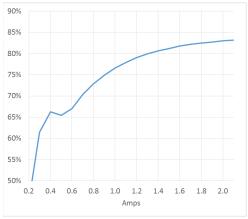

Fig. 4: Channel 4, 1.8V Efficiency

Fig. 6: Channel 2, 1.5V Load Regulation

© 2016 Exar Corporation 5/14 Rev. 1.0.1

Fig. 7: Channel 3, 2.5V Load Regulation

Fig. 8: Channel 4, 1.8V Load Regulation

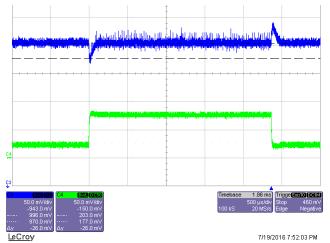

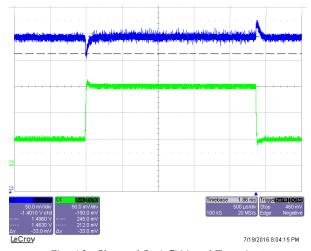

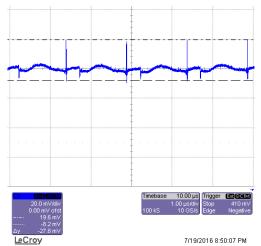

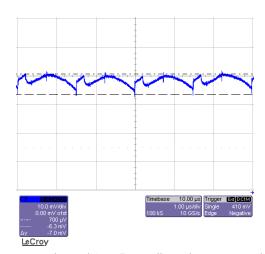

Fig. 9: Channel 1, 1.0V Load Transient 25% - 75% 5A/us

Fig. 10: Channel 2, 1.5V Load Transient 25% - 75% 5A/us

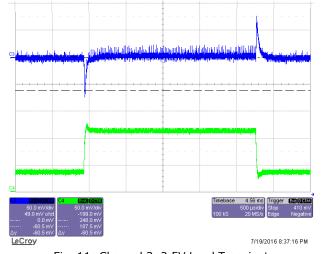

Fig. 11: Channel 3, 2.5V Load Transient 25% - 75% 5A/us

Fig. 12: Channel 4, 1.8V Load Transient 25% - 75% 5A/us

© 2016 Exar Corporation 6/14 Rev. 1.0.1

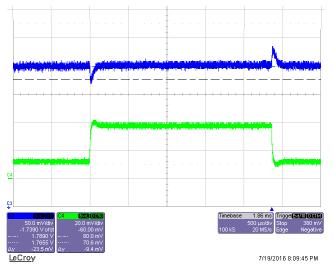

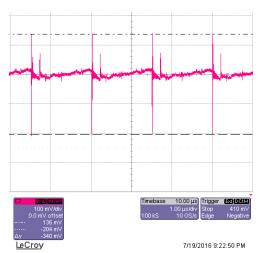

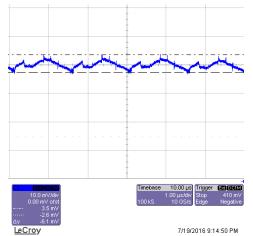

Fig. 13: Channel 1, 1.0V Full Load Output Ripple

Fig. 15: Channel 3, 2.5V Full Load Output Ripple

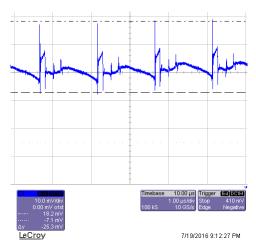

Fig. 17: Input Cap Ripple

Fig. 14: Channel 2, 1.5VV Full Load Output Ripple

Fig. 16: Channel 4, 1.8V Full Load Output Ripple

© 2016 Exar Corporation 7/14 Rev. 1.0.1

# **BILL OF MATERIAL**

| Ref.                                       | Qty | Manufacturer          | Part Number        | Size         | Component                                |

|--------------------------------------------|-----|-----------------------|--------------------|--------------|------------------------------------------|

| РСВ                                        | 1   | Exar                  | 146-6730-01        |              | XRP77114EVB_IND_V09_VER2                 |

| U1                                         | 1   | Exar                  | XR7714ILB-F        |              |                                          |

| U2                                         | 1   | Exar                  | XRP2997IDBTR-F     | SOICD B08    | 2A, DDR I/II/II Bus Term.<br>Regulator   |

| Q1,Q2,Q4                                   | 3   | Diodes, Inc.          | DMN2050LFDB        | U-DFN2020-6  | Dual N-Ch. MOSFET, 20V,4.5A,<br>45mOhm   |

| Q3                                         | 1   | Diodes, Inc.          | DMN2300UFL4        | X2-DFN1310-6 | Dual N-Ch. MOSFET,<br>20V,2.11A, 195mOhm |

| D1,D2,D3,D4                                | 4   | Diodes, Inc.          | SD101AWS           | SOD-323      | SMT Barrier Diode, 60V, 15mA             |

| L1,L2                                      | 2   | Wurth<br>Elektronik   | 7440620015         | 6.8X6.8MM    | SMD Inductor 1.5uH, 4.3A,<br>14.0 mOhm   |

| L3,L4                                      | 2   | Wurth<br>Elektronik   | 74408943047        | 4.8X4.8MM    | SMD Inductor 4.7uH, 2.2A,<br>45.0 mOhm   |

| C2,C9,C22                                  | 3   | MURATA                | GRM31CR60J107ME39L | 1206         | CERAMIC CAP. 100uF, 6.3V,<br>X5R, 20%    |

| C10, C12, C15, C19                         | 4   | MURATA                | GRM31CR61A476KE15L | 1206         | CERAMIC CER, 47uF, 10V, X5R, 10%         |

| C1,C7,C18,C21                              | 4   | MURATA                | GRM31CR71H475KA12L | 1206         | CERAMIC CAP., 4.7uF, 50V,<br>X7R, 10%    |

| C4,C5,C8,C17                               | 4   | MURATA                | GRM21BR71E475KA73L | 0805         | CERAMIC CAP., 4.7uF, 25V,<br>X7R, 10%    |

| C3,C13,C14                                 | 3   | MURATA                | GRM21BR71C225KA12L | 0805         | CERAMIC CAP., 2.2uF, 16V,<br>X7R, 10%    |

| C6,C11,C16,C20                             | 4   | MURATA                | GRM155R71E104KE14D | 0402         | CERAMIC CAP., 0.1uF, 25V,<br>X7R, 10%    |

| R1,R2                                      | 2   | PANASONIC             | ERA-3AEB104V       | 0603         | Resistor 100.0K Ohm, 0.1%<br>1/10W, SMD  |

| R3                                         | 1   | PANASONIC             | ERJ-3EKF6802V      | 0603         | Resistor 68.0K Ohm,<br>1/10W,1%,SMD      |

| R4                                         | 1   | PANASONIC             | ERJ-3RQF1R0V       | 0603         | Resistor 1.0 Ohm,<br>1/10W,1%,SMD        |

| J7,J1,J8,J2,J4,J9,J10,J<br>3,J16,J5,J6,J15 | 12  | Vector<br>Electronics | Vector Electronics | .042" Hole   | PCB Pin                                  |

| TP1,TP0,TP3,TP4,TP2                        | 5   | Wurth<br>Electronics  | 61300111121        | Test Point   | Test Point                               |

| 1-SCL,GND,SDA                              | 1   | Wurth<br>Electronics  | 61300311121        | Test Point   | 3 PIN HEADER                             |

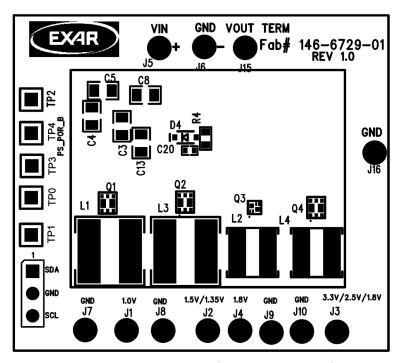

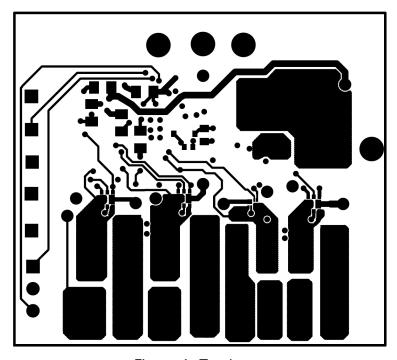

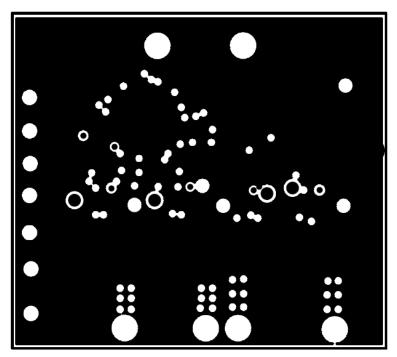

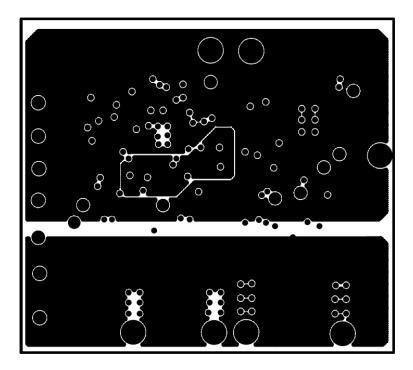

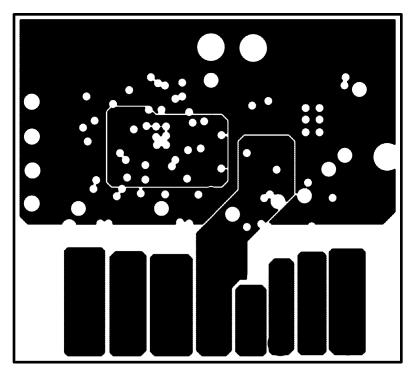

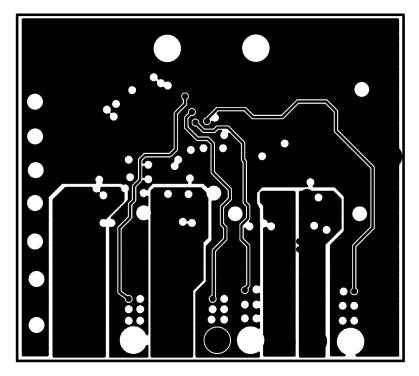

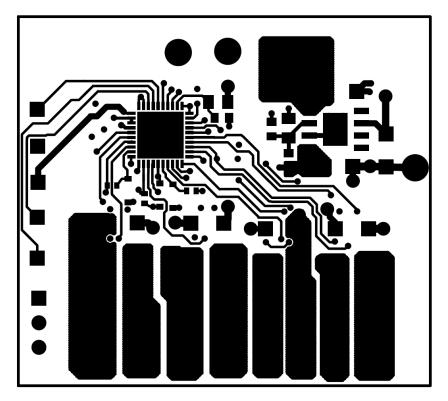

# **EVALUATION BOARD LAYOUT (FOR REFERENCE)**

Figure 3: Component Placement Top Side

Figure 4: Top Layer

© 2016 Exar Corporation 10/14 Rev. 1.0.1

Figure 5: Ground Plane

Figure 6: Mid-Layer

© 2016 Exar Corporation 11/14 Rev. 1.0.1

Figure 7: Mid-Layer 2

Figure 8: Mid-Layer 3

© 2016 Exar Corporation 12/14 Rev. 1.0.1

Figure 9: Bottom Layer

#### **DOCUMENT REVISION HISTORY**

| Revision | Date       | Description                            |

|----------|------------|----------------------------------------|

| 1.0.0    | 06/22/2016 | Initial release of document            |

| 1.0.1    | 07/19/2016 | Added electrical characteristic curves |

#### FOR FURTHER ASSISTANCE

Email: powertechsupport@exar.com

customersupport@exar.com

Exar Technical Documentation: http://www.exar.com/TechDoc/default.aspx?

#### **EXAR CORPORATION**

#### **HEADQUARTERS AND SALES OFFICES**

48720 Kato Road

Fremont, CA 94538 - USA

Tel.: +1 (510) 668-7020

Fax: +1 (510) 668-7030

www.exar.com

#### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.